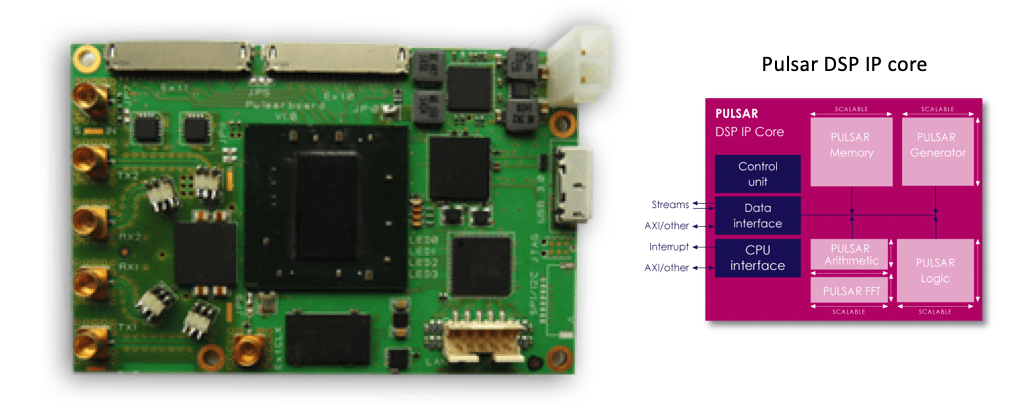

PULSAR SDR Platform

The development of the Simpulse PULSAR SDR platform began in the early days of Simpulse. Now patented, this platform built around a powerful and scalable digital signal processing (DSP) engine is constantly evolving. It is optimized to host the development of new architectures of SDR (Software Defined Radio) digital processing solutions. This combines hardware computing power with software flexibility, ensuring that Simpulse products are scalable, easy to customize and to improve. Simpulse also developed a comprehensive patented Pulsar toolchain for an automatic implementation of signal processing functions.

Hardware Scalable

PULSAR hardware is scalable, making it possible to optimize the system according to the constraints of cost, performance and power consumption imposed by the application.

- Hardware architecture can be adapted to the application to manage different levels of system complexity (long / short range, high / low speed ...)

- Highly parallel SIMD (multiple data single instruction) processor architecture

- Low power solution. A hardware operator is designed to reduce power consumption depending on data rate requirements

- Optimized for FPGA and ASIC targets

Programmable

The PULSAR hardware is programmable, resulting in a very flexible software-defined radio (SDR) technology platform.

- Flexible signal processing circuits for high development efficiency (20 times better than wired designs)

- Optimized to design new waveform and protocols (ie Simpulse libraries) or even multi-standard applications (ie IoT)

- Enables constant improvement in application performance through simple software updates